2003 年 10 月 30 日 独立行政法人 理化学研究所 日本電気株式会社

# 固体素子を用いた量子ビット論理演算回路を世界で初めて実現

## - 量子コンピュータを構成する基本回路を完成 -

独立行政法人理化学研究所(野依良治理事長)と NEC (金杉明信代表取締役社長) は、固体素子で構成される量子コンピュータの基本素子 2 個を結合することで"量子論理演算回路"を構成し、その動作に世界で初めて成功しました。今回の成果は量子コンピュータの実現に向けた大きな一歩と言えます。これは NEC 基礎研究所/理研フロンティア研究システム(巨視的量子コヒーレンス研究チーム: リーダー 蔡 兆申 (ツァイ・ヴァオシェン))の共同研究による成果です。

現在のコンピュータをはるかに越えた情報処理能力を持つと期待される量子コンピュータは、「量子ビット」と呼ばれる「0」と「1」を重ね合わせた物理状態を演算単位として使います。その演算は、量子ビットの物理状態に回路操作を施すことによって実行されますが、量子ビット1個の状態を制御する回路と2個の量子ビットの間で論理演算を行う回路との組み合わせにより、任意の量子演算が実現できることが理論的に証明されています。

NEC では 1999 年、超伝導体を用い、固体量子ビット 1 個の回路動作に世界で初めて成功しました。さらに 2003 年 2 月には NEC と理研の共同研究チームが、前記の量子ビットを 2 個結合させた素子を用いて量子コンピュータの実現に不可欠な量子絡み合い状態の生成に成功しました。しかし、どうすれば 2 個の量子ビット間で論理演算を実現できるかは明らかではありませんでした。

今回、2個結合した量子ビットを各々自在に制御できる素子構造と、これを用いて 論理演算を行うのに必要となる特有のパルス信号列を新たに考案することで、制御付 き否定ゲートと呼ばれる2ビットの論理演算を実現し、それが期待通りに動作するこ とを実証しました。

1量子ビット回路と2量子ビット論理演算回路の固体素子での実現は、量子コンピュータが集積化可能な固体素子により構成可能であることを初めて明らかにするもので、これにより、固体量子コンピュータを実現するための基本回路が揃ったと言えます。今後は、これらの回路の集積化・量子計算アルゴリズムの実証といった、新しい段階の研究に取り組み、量子コンピュータの実現を目指していきます。

本研究成果の詳細は、英国の科学雑誌『nature』(10月30日号)に掲載されます。

#### 1.背 景

電子や原子のような微小な世界では、私たちが日常生活で経験する物理法則とはまったく異なった量子力学と呼ばれる物理法則が支配しており、粒子は同時に波としての性質を持つようになります。電子を例に取ると、量子の世界では電子波として空間的に広がった存在になります。

量子コンピュータとは、このような電子などの量子力学的状態を利用して演算す

るコンピュータです。この技術が実現すれば、現在のコンピュータをはるかに越える計算能力を持つと期待されています。(例えば、現在のコンピュータでは数千年もかかるような数百桁の数字の素因数分解が数十秒で解けると考えられています。)量子コンピュータは、革新的なアイデアであったものの、実用的な応用は未開拓でした。しかしながら1994年、AT&Tリサーチ(米国)のピーター・ショー(Peter Shor)によって具体的な素因数分解のアルゴリズムが発見されて以来、暗号解読や膨大な情報処理演算に有効と期待され、研究が盛んになってきました。

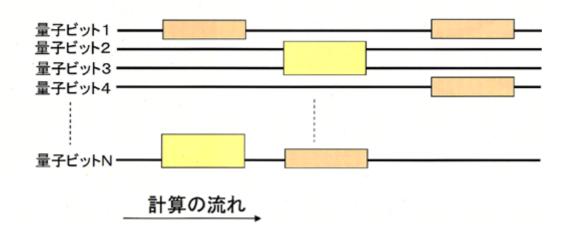

量子コンピュータは、具体的には「量子ビット」と呼ばれる演算単位で計算します。量子ビットは、"0"と"1"という 2 つの物理状態を波として重ね合わせることで同時に実現します。この重ね合わせができるのは、原子や分子などが量子力学的な波の性質を持っているからです。一方、量子演算はその量子ビットの物理状態に対して回路操作を施すことによって行われます。この回路操作を説明したのが図 1aです。1つの量子ビットは 1本の線に対応し、線上の四角は量子回路を表します。左側の線を入力ビットとすると、右側の線は、その入力に対してある特定の回路操作を施した後の量子ビットを表します。図 1aの量子回路は 1つの量子ビットに対して作用する量子回路、あるいはそれ以上の数のビットに対して作用するものも考えられます。実際の量子計算は図 1cに示したように、複数の量子ビットに次々と回路操作を施していくことで実行されるのです。

さて図 1cに示した量子回路の実行パターンは当然解くべき問題によって変わってきます。従って必要となる量子回路も幾らでもありそうな気がしますが、実はどんなに複雑なアルゴリズムでも、それは、1 量子ビットの状態を制御する 1 ビット回路と、二つの量子ビットの間で論理演算を行う 2 ビット回路の 2 つに分解することが出来るということが理論的に証明されています。つまり任意の量子計算はこの二つの量子回路さえ実現できれば、原理的には遂行可能なのです。これは現代のコンピュータが NAND 回路や NOR 回路の基本回路のみにより構成されているのと同じです。

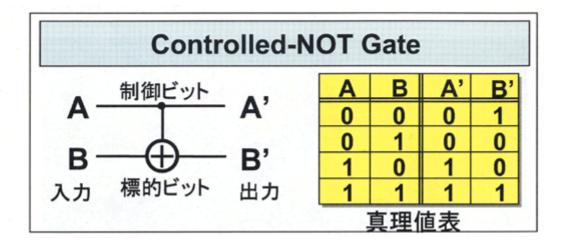

NEC は 1999 年、超伝導電子対(超伝導状態にある電子は 2 個で対をなして動き回ることが知られています)を入れる微小な箱を超伝導体で作製し、近接した制御電極への電圧パルスによりこの電子対箱中の電荷量を制御することで、固体素子による量子ビット一個の動作に世界で初めて成功しています。その後、幾つかの研究室でも同様な研究成果は実現していますが、量子コンピュータを構成するのに必要な上述の二種類の量子回路のうちの 2 番目の 2 ビット論理演算回路を固体素子で実現するには至っていませんでした。当グループは本年 2 月に、キャパシタンスで結合した超伝導 2 量子ビット素子を用いて、量子コンピュータに必要な量子絡み合い状態の実現に成功しました。今回、2 個結合した量子ビットを各々自在に制御できる素子構造と、これを用いて論理演算を行うのに必要となる特有のパルス信号列を新たに考案することで、2 ビット論理演算回路、具体的には図 2 に示した制御付き否定回路の実現を目指しました。この回路は図中の真理値表で示したように、A、B二つの量子ビットの入力に対し、A (制御ビットと呼ぶ)が"0"の時のみ、もう一方の B (標的ビットと呼ぶ)の状態を反転させるという働きを持つものです。

### 2. 研究成果

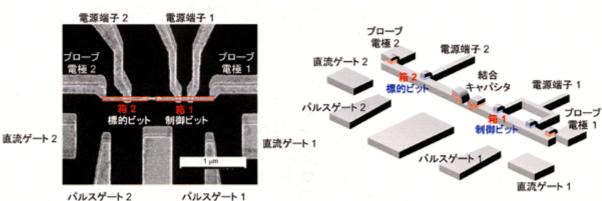

研究グループでは、キャパシタによって結合した2つの量子ビットからなる回路を用いて、直流電圧およびパルス電圧によって制御付き否定回路を実現する方法を提案し、それが期待通りに論理演算動作をすることを実験的に確認しました。実際に用いた試料の写真を図3aに、その模式図を図3bに示します。素子の構成は図3bのように、量子ビットを構成する二つの超伝導電子対箱が微小な結合キャパシタ(コンデンサ)により結合しており、それぞれの箱には状態制御用の直流電極およびパルス電極が取り付けられております。各電子対箱はトンネル接合(図3b模式図の青い部分)を介し電源端子に接続され量子ビットを形成しています。右の量子ビット(箱1、または制御ビット)の電源端子は、2点で電子対箱に接続していますが、これは実験の都合による構造で、1点で接続している場合と本質的には同じです。また、各量子ビットにはトンネル電流によってその状態を読み出す為のプローブ電極が備わっています。素子の全体の大きさは図3bから分かるように1ミクロン強で、量子ビットとなる箱の大きさはそれぞれ0.9ミクロン×0.05ミクロン程度であります。この素子は全てアルミ薄膜で構成され、素子の作製は最先端の微細加工技術によってなされました。

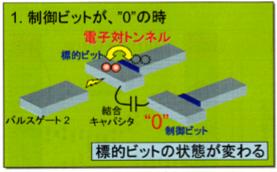

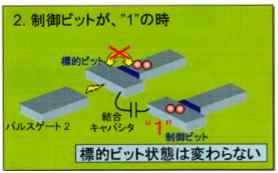

ここで図 3c を用いて制御付き否定回路の動作原理を簡単に説明します。なお図 3c では簡単化のため、プローブ電極、直流電極、制御ビットのパルス電極は省略し ています。量子ビットの"0"と"1"の二つの状態は、箱内の超伝導電子対の数が異な る状態を使い表現します。この場合"0"は余剰超伝導電子対がない状態、"1"は余剰 超伝導電子対が1個ある状態です。各量子ビットに適宜な高さ(電圧)の電圧パル スを素早く印加し、量子ビットを"0"と"1"の中間状態にバイアスすると、箱中の余 剰超伝導電子対が振動を始め、その個数は0個と1個の間を繰り返すことになりま す。この時、電圧パルスの印加を速やかにストップすると、その時点での個数状態 が保持される為、電圧パルスの印加時間で箱中の余剰電子対の個数を自在に変える ことができます。図 3c の上半分に示されているように、制御ビットが"0"の場合、 制御ビットの箱には余剰電子対は無い為、キャパシタで接続された標的ビットには エネルギ的な影響はありません。標的ビットに上述のパルス電圧を印加し、適当な パルス印加時間を選ぶ事で、標的ビットの状態を"0"から"1"に変化させることがで きます。一方、図 3c の下半分に示されているように、制御ビットが"1"の場合、制 御ビットの箱に余剰電子対が存在する為に、キャパシタを介して標的ビットの電子 対箱のエネルギ状態が高くなり(図3cに模式的に示してあります)、標的ビットの 電子対箱に電子が入ることができなくなります。従って、先ほどと同じパルス電圧 を加えても、標的ビットの状態を変化させることはできなくなります。以上をまと めると標的ビットは制御ビットが"0"の状態の時のみその状態を反転させることに なり、所望の条件付ゲート動作が実現されることになります。

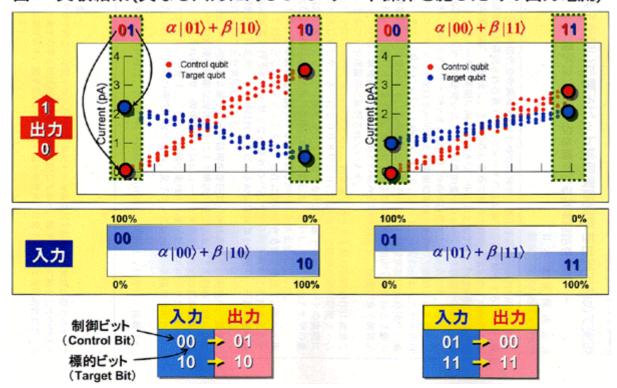

図4は実験データです。実験は"0"と"1"の重ね合わせ状態も含めて様々な入力状態を準備し、それらに上述のゲート動作を施し、その出力を検出しました。左側のグラフでは入力状態として制御ビットに"0"と"1"の重ね合わせ状態、標的ビットに"0"の状態を準備します。横軸の変化は制御ビットの"0"と"1"の状態の強さ(振幅)を徐々に変化させて重ね合わせた入力状態を準備したことに対応します。これに対応して各々の出力ビットも"0"と"1"の重ね合わせ状態として出力されます。縦軸に

はプローブ電極を通して流れる出力電流をプロットしてあり、電流が高いということはその時の量子ビットの状態がより"1"に近いことを意味します。

制御と標的ビットの2状態を簡便な表現で、例えば"00"と表現します、この場合 左側が制御ビットの状態、右側が標的ビットの状態を表します。図4左図の両端か ら、入力"00"に対して"01"の出力が、入力"10"に対しては"10"が獲られていること が分かります。これは制御付き否定回路として期待される動作です。また制御ビッ トに重ね合わせ状態を入力した場合を見ると、制御ビットが"0"になる場合に標的ビ ットが反転するので、出力としても"01"と"10"の重ね合わせの状態が生成されるこ とになります。これを反映して出力電流は"01"と"10"の状態の強さが重ね合わさっ たものとなり、入力"00"に対する出力"01"から入力"10"に対する出力"10"へとなだ らかに変化しているのが判ります。"01"と"10"の重ね合わせは絡み合い状態と呼ば れる量子計算には不可欠な量子状態です。この状態はグラフの上部に示した2個で 1組のオセロの駒を使ってたとえることができます。ここでオセロの駒は各々の量 子ビットに対応し、片方は白("0")を上にして、もう片方は黒("1")を上となる ように目には見えない絡み合い棒で接続され、この棒を軸として超高速で回転して いる状態と比喩的に表すことができます。これをテーブルの上に落とす(観測する) と、片方が白("0")の時には必ずもう片方は黒("1")となります。一方、右側の グラフは入力として、"01"と"11"の重ね合わせ状態を準備した実験の結果です(標 的ビットの入力が常に"1"で、制御ビットを"0"から重ね合わせ状態を経て"1"へと変 化させています)。標的ビットの出力が先ほどの場合とは反転しており、図中の両 端から"01"の入力に対して"00"が、"11"の入力に対して"11"が得られており、制御 付き否定回路の期待される動作がなされていることが分かります。また重ね合わせ 状態についても同様に、出力には"00"と"11"の重ね合わせによる絡み合い状態が生 成されています。出力電流もこれを反映して、"00"と"11"の状態の強さが重ね合わ さったものとなっており、入力"01"に対する出力"00"から入力"11"に対する出力 "11"へとなだらかに変化しているのが判ります。上部のオセロで示したように、今 度は片方が白("0")であればもう片方も白("0")となるように接続されて回転し ている状態でたとえることができます。テーブルに落とした時、片方が白("0")で あれば、もう片方も白("0")、片方が黒("1")であればもう片方も黒("1")とな ります。以上の結果は、固体量子ビット2個を用いて、2ビット演算回路を実現し、 制御付き否定論理演算を世界で初めて示したものであり、量子コンピュータ実現へ 大きく前進するものです。

#### 3. 今後の展開

今回、結合量子ビットを用いて、2量子ビットの制御付き否定回路動作の実証に成功しました。これで量子コンピュータを構成するのに必要な二種類の量子回路の全ての量子演算が可能になったことになります。今後は、今回の2ビット量子回路と1ビット量子回路トを用いて、量子アルゴリズムの実証と量子ビットの更なる集積化を目指します。

## (問い合わせ先)

独立行政法人理化学研究所

フロンティア研究システム 単量子操作研究グループ 巨視的量子コヒーレンス研究チームチームリーダー NEC 基礎研究所 主席研究員

蔡 兆申

Tel: 029-850-1161/Fax: 029-856-2624

## (報道担当)

独立行政法人理化学研究所 広報室

Tel : 048-467-9272 / Fax : 048-462-4715

Mail : koho@riken.jp

図1a: 1量子ビットゲートの表記法

入力 A — 量子ゲート — 出力 A'

図1c: 量子計算の流れ

図2: 制御否定ゲート

図3b: デバイス構造模式図

図3a: デバイスSEM写真

図3c: デバイス動作原理

# 図4: 実験結果(異なる入力に対しCNOTゲート操作を施した時の出力電流)